Product Summary

The K9F1G08U0A-PCB0 is a 128M x 8 Bit memory organized as 65,536 rows(pages) by 2112x8 columns. Spare 64 columns are located from column address of 2048~2111. A 2112-byte data register and a 2112-byte cache register are serially connected to each other. The serially connected register of the K9F1G08U0A-PCB0 is connected to memory cell arrays for accommodating data transfer between the I/O buffers and memory cells during page read and page program operations. The memory array is made up of 32 cells that are serially connected to form a NAND structure. Each of the 32 cells resides in a different page. A block consists of two NAND structured strings. A NAND structure of the K9F1G08U0A-PCB0 consists of 32 cells. Total 1081344 NAND cells reside in a block. The program and read operations are executed on a page basis, while the erase operation is executed on a block basis. The memory array consists of 1024 separately erasable 128K-byte blocks. It indicates that the bit by bit erase operation is prohibited on the K9F1G08X0A.

Parametrics

K9F1G08U0A-PCB0 absolute maximum ratings: (1)VIN/OUT -0.6 to + 2.45 -0.6 to + 4.6V; (2)VCC -0.2 to + 2.45 -0.6 to + 4.6; (3)TBIAS -10 to +125 ℃; (4)TSTG -65 to +150 ℃; (5)Ios 5 mA.

Features

K9F1G08U0A-PCB0 features: (1)Command/Address/Data Multiplexed I/O Port; (2)Hardware Data Protection. Program/Erase Lockout During Power Transitions; (3)Reliable CMOS Floating-Gate Technology. Endurance : 100K Program/Erase Cycles. Data Retention : 10 Years; (4)Command Register Operation; (5)Cache Program Operation for High Performance Program; (6)Intelligent Copy-Back Operation; (7)Unique ID for Copyright Protection.

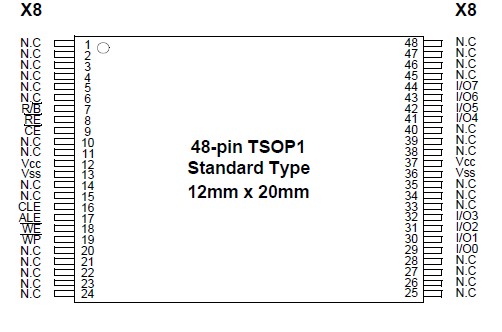

Diagrams

|

K9F1208D0A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

K9F1208Q0A-XXB0 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

K9F1208Q0B |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

K9F1208R0B |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

K9F1208U0A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

K9F1208U0A-VCB0 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))